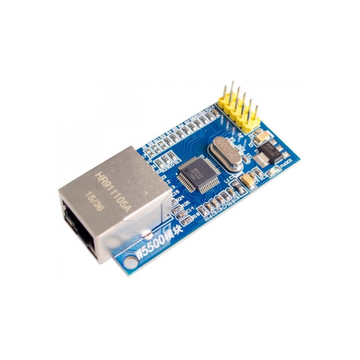

W5500 SPI Ethernet Module

W5500 SPI Ethernet Module

The W5500 chip is an embedded Ethernet controller that facilitates hardwired network connections for embedded systems via SPI (Serial Peripheral Interface). This chip is particularly useful for users requiring stable internet connectivity, as it integrates TCP/IP Stack, 10/100 Ethernet MAC and PHY into a single chip. The W5500 chip supports various protocols such as TCP, UDP, IPv4, ICMP, ARP, IGMP, and PPPoE, which have been widely used in many applications.

The W5500 also features a 32Kbytes internal buffer as its data communication memory, making it easy for users to implement Ethernet applications using simple socket programming instead of dealing with complex Ethernet controllers. The chip supports 8 independent hardware sockets and an efficient SPI protocol, allowing for high-speed network communication at 80 MHz. Additionally, the W5500 includes power-saving features such as Wake on LAN (WOL) and a power-down mode.

Note: While this device can be used with an ESP32 over the SPI Bus, it is not compatible with the builtin hardware Ethernet MAC that exists in the ESP32.

Features

- Supports following Hardwired TCP/IP Protocols : TCP, UDP, ICMP, IPv4, ARP, IGMP, PPPoE

- Supports 8 independent sockets simultaneously

- Supports Power down mode

- Supports Wake on LAN over UDP

- Supports High Speed Serial Peripheral Interface(SPI MODE 0, 3)

- Internal 32Kbytes Memory for Tx/Rx Buffers

- 10BaseT/100BaseTX Ethernet PHY embedded

- Support Auto Negotiation (Full and half duplex, 10 and 100-based)

- Not support IP Fragmentation

- 3.3V operation with 5V I/O signal tolerance

- LED outputs (Full/Half duplex, Link, Speed, Active)

- Chipset: W5500

- Module size: 55mm x 28mm

- Power supply: 3.3v /5v

- SPI clock frequency(MAX): 80MHz

- Work current(typical): 128mA

Our goal is to ensure a smooth and transparent delivery process for your convenience and satisfaction. Here are the details of our delivery process:

Processing time

The processing time begins on the day you place your order. We process orders within 1-3 business days (Monday to Friday, excluding public holidays).

Shipping Costs and Total delivery time = processing time + delivery time

-

Free standard shipping on orders over $129.

-

$10 Flat rate standard shipping on orders under $129.

-

$15 for Express Shipping for all orders

-

For orders with bulky or heavy items exact shipping costs will be calculated at checkout.

|

Shipping Name |

Handling Time |

Transit Time |

|

Standard Shipping |

1-3 days (Monday to Friday) |

3-7 days (Monday to Friday) |

|

Express Shipping |

1-3 days (Monday to Friday) |

3-5 days (Monday to Friday) |

Order cut off Time: 5:00 pm (GMT+10:00) Australian Eastern Standard Time (Sydney)

Please note:

-

Delivery times are affected by public holidays as manufacturers and courier services operate on a restricted basis. This is beyond our control. Normal service will resume immediately after each public holiday.

-

Incorrect address details and other problems may lead to delays in delivery.

Tracking your order

When your goods are dispatched, you should receive an email notification from us with a tracking number.

For tracking issues, please contact us at info@dialedin.com.au or call us at +61 0407090435.

Carrier

We use Australia Postage for most deliveries.

Changing your address

We cannot change the delivery address once the order has been shipped. If you wish to change your delivery location, please contact us within 24 hours of placing your order at info@dialedin.com.au or call us on +61 0407090435. Please note that we process and dispatch orders within one working day of placing the order.

If your order has already been dispatched via Australia Post, you can login to your AusPost MyPost account and request for the parcel to be redirected to a new address. We are unable to make any changes after dispatch.

Cancellations

If you change your mind before you receive your order, we can accept cancellations at any time before the order is shipped. Please refer to our refund policy if an order has already been shipped.

Parcels damaged in transit:

If you find that a parcel has been damaged in transit, you must refuse the parcel from the courier and contact our customer service team. If the parcel was delivered in your absence, please contact customer service to find out how to proceed.

For further inquiries, you can reach us at:

Phone: +61 0407090435

Email: info@dialedin.com.au

Address: PO Box 8002, Reservoir, Victoria, 3073, Australia